触发器是构造时序逻辑电路的核心,本文分析了触发器电路的构造过程、工作原理,帮助读者看懂并用好“车轮”。

一、电平控制的SR触发器

1.1 二值锁存电路(双稳态存储单元电路)

作为构造SR锁存器的重要前体,二值锁存电路不是一种具有实用价值的数字电路,而仅存在于逻辑概念当中。如图1所示,二值锁存电路由两个首尾相连的非门构成,上下两个非门的输出线分别对应逻辑变量Q和QN,且二者总保持互补关系。如图1下半部所示,二值锁存电路仅存在两种稳定且能自我保持的电平状态,这是构造时序逻辑电路的重要前提。然而,二值锁存电路的电平状态虽然能够自我保持,但不能由外界控制。为此,锁存器的概念应运而生。

1.2 SR锁存器

(1) SR锁存器的构造过程

“与‘0’或‘1’”作为一种控制逻辑变量的常用方法,可有效解决二值锁存电路电平状态不可由外界控制的问题。如图2所示,在二值锁存电路每个非门的输出端串入一只二输入的或门或与门,即可实现外界对Q和QN逻辑状态的有效控制。图2最底部所示,即由恒等变换获得的SR锁存器电路结构,其中由与非门构成的电路结构(下文论述均以此为基础)在教材中出现的频率最高。

(2) SR锁存器的工作原理

图3 锁存器的工作原理

如图3(a)所示,SR锁存器的两个输入端均接收到低电平。如果t0时刻之前两个输出端口为互补电平(图3(a)中,右上角和左下角两种情况),那么此时的SR锁存器相当于一个二值锁存电路,保持旧有的输出电平;如果t0时刻之前两个输出端口同为低电平或高电平(图3(a)中,左上角和右下角两种情况),那么由于与非门的作用,两输出端口的输出电平将向与各自旧状态相反的电平跳变,此时半导体器件的分散性将造成两个输出端口之间的逻辑竞争。逻辑竞争的结果是随机的,由于锁存器的保持作用,两输出端口最终的电平状态可能被保持在图3(a)右上角和左下角两种情况中的任何一种。

如图3(b)所示,SR锁存器两个输入端接收到的不全为低电平。由于非门和与非门的共同作用,两输出端最终的电平状态均是确定的,不存在随机的情况。

1.3 电平控制的SR触发器

图4 同步SR触发器

从上一节论述可知,SR锁存器通常仅在输入端(S,R)==(1,0)或(0,1)时转换输出电平,而在(S,R)==(0,0)时保持输出电平状态不变(两种竞争的情况除外)。基于SR锁存器这一动作特点,可在其前端串入与门,依靠同步时钟脉冲控制锁存器的动作时刻,这样的电路被称作电平控制的同步SR触发器,如图4所示。

二、主从SR触发器

2.1 主从触发器的工作原理

(1) 电平控制型SR触发器的跟随特性

如图3(c)所示(见“1.2节(2) SR锁存器的工作原理”),除去(S,R)==(0,0)的情况,电平型同步SR触发器的输出电平实质上是在时钟信号CLK的控制下,定时跟随输入端SR的电平状态而变化,这可被看作电平型SR触发器的一种跟随特性。

(2) 主从SR触发器的构造过程、工作时序

图5 主从上升沿SR触发器

如图5(a)所示,时钟上升沿动作的主从SR触发器由两只具有互补时钟信号的电平型SR触发器前后级联构成,前、后两级触发器分别充当主触发器和从触发器。

其中,主触发器在CLK==0期间,根据输入端S、R的电平状态,对输出端Qm、QmN的电平状态做出相应的改变;而在CLK==1期间,主触发器将锁定其输出端Qm、QmN的电平状态。相反地,从触发器在CLK==0期间,锁定其输出端Qs、QsN的电平状态;而在CLK==1期间,从触发器会将主触发器的输出电平跟随输出到其输出端Qs、QsN上。

主、从触发器电平状态的具体传递过程如时序图5(b)所示:

1) 在CLK==1期间,主触发器将CLK上升沿之前最后一刻(即图5(b)深蓝色时间段的最后一刻)的电平状态锁存到其输出端Qm、QmN(图5(b)浅蓝色时间段)上,再经由主、从两触发器之间的连线传递给从触发器,最终由从触发器跟随输出(图5(b)红色时间段);

2) 在CLK==0期间,从触发器将CLK下降沿之前最后一刻所输出的电平状态锁存到其输出端Qs、QsN(图5(b)橙色时间段)上。因此,从触发器在图5(b)橙色时间段内的输出电平,总与其左侧紧邻的红色时间段相同;

3) 在CLK==0期间,主触发器输出端Qm、QmN的电平状态将根据输入端S、R的电平状态实时变化(图5(b)深蓝色时间段)。而此时处于锁存状态的从触发器的输出电平不受主触发器影响(图5(b)深蓝色时间段);

4) 需要特别指出:虽然主从触发器输出端电平是在CLK信号的边沿时刻发生动作的,但是主触发器在CLK==0期间,仍是作为一个电平型触发器而存在的。这意味着主触发器在CLK上升沿及以后时间段锁存的电平状态,是CLK==0全时间段内S、R电平状态作用于主触发器产生的结果,而不是由CLK上升沿这个单一时刻的S、R电平状态决定的。这是主从触发器与边沿触发器的根本区别。

综上,在时钟上升沿动作的主从SR触发器当中,主触发器负责根据输入端S、R的电平状态,决定主从触发器整体的输出电平,而从触发器仅负责保持、反馈,并跟随输出该电平。

图6 时钟下降沿动作的主从SR触发器

交换主、从两触发器的CLK信号,可构造时钟下降沿动作的主从SR触发器,如图6所示。

三、其它主从触发器

在主从SR触发器的主触发器输入端(S,R)前部串入特定的组合电路,可构造出D、JK、T等其它功能的主从触发器。需要指出,这几种触发器是以主从SR触发器为基础衍生而来的,二者在从触发器的结构上没有区别,从触发器始终负责跟随输出主触发器的输出电平。

3.1 主从D触发器

图7 由主从SR触发器构造D触发器

需要指出,对处于触发状态的D触发器而言,它的输出电平(Q,QN)会持续跟随(D,~D)。因此,主触发器在进入锁存状态前最后一刻的输出电平只与CLK边沿时刻输入端D的电平状态有关,与触发时间段内其它任何时刻输入端D的电平状态无关。换言之,主从D触发器的输出电平不仅是在CLK边沿时刻发生动作的,而且是在CLK边沿时刻才被确定并锁存的,因此主从D触发器是一种边沿触发器。

3.2 主从JK触发器

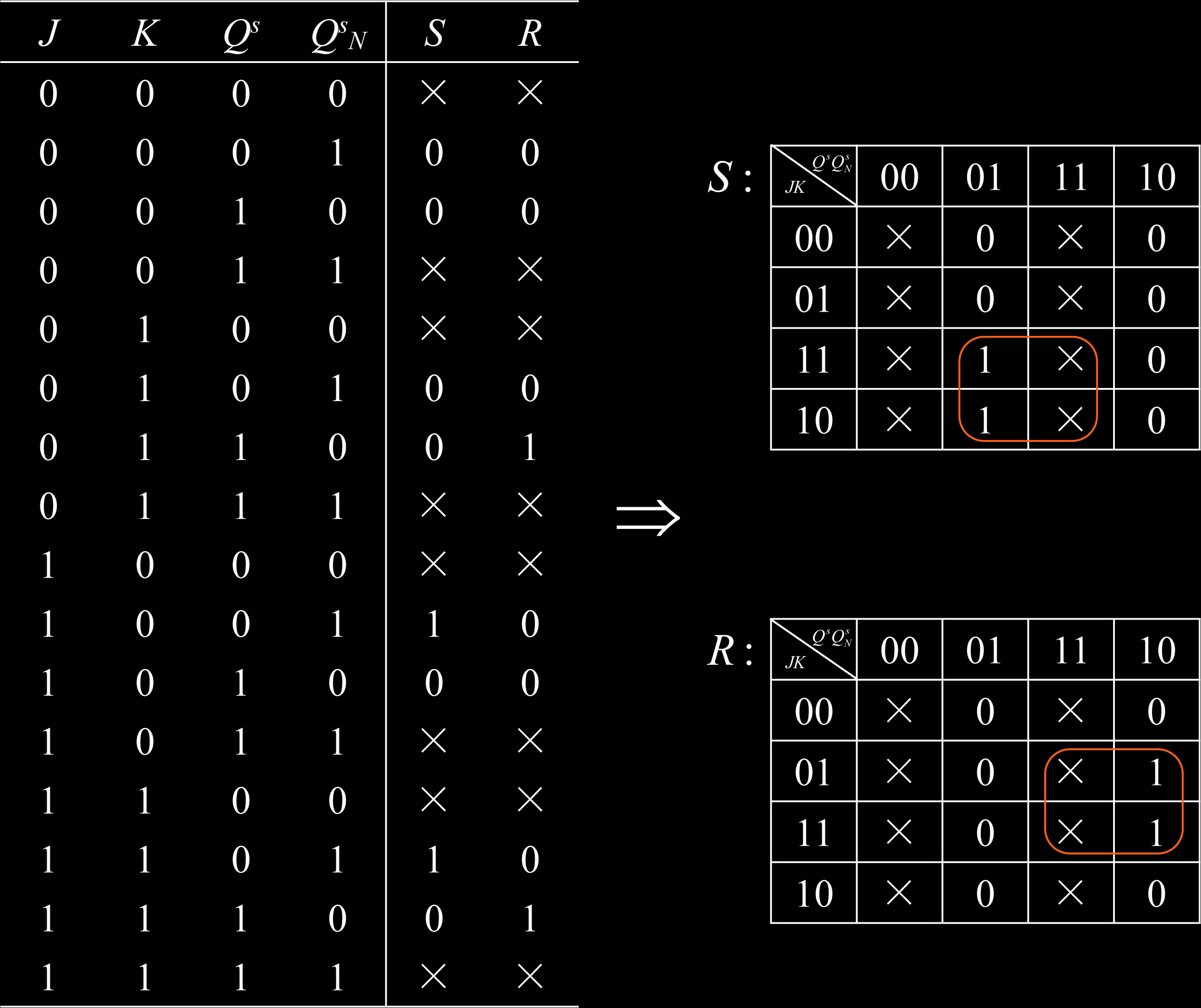

图8 由主从SR触发器构造JK触发器

对于主从JK触发器而言,当主触发器处于触发状态时,它输出的新电平状态是以从触发器锁存的旧输出电平为准的,且主触发器的输出电平在一个CLK周期中最多变化1次,如图9所示。这被称作主从JK触发器的“一次变化特性”。感兴趣的读者,请访问站内视频:BV1np4y1y7Yj 5.4-2脉冲触发方式的动作特点07:01/11:51.

3.3 主从T触发器

图10 由主从SR触发器构造T触发器

如图10 (c)可知,主从T触发器在电路结构上等同于将主从JK触发器的J、K两个输入端一同连接到T输入端。因此,主从T触发器同样具有与主从JK触发器类似的“一次变化特性”,如图11所示。

四、边沿触发器

边沿触发器即在CLK边沿时刻输出电平判断和跳变的触发器。边沿触发器输出电平的次态仅取决于CLK边沿时刻的输入电平和输出电平的初态,具有相较于电平型触发器、主从触发器更强的抗干扰能力。3.1节所述的主从D触发器是一种边沿触发器,在它输入端D的前端串入特定的组合逻辑电路,可获得具有SR、JK、T逻辑功能的边沿触发器。

4.1 边沿SR触发器

图12 由主从D触发器构造SR边沿触发器

如图12 (a)所示,因为SR触发器的输出端Q和QN不是互补输出,所以边沿SR触发器的Q和QN端只能分别由两个相互独立的主从D触发器的正相输出端分别构造,如图12 (c)所示。

4.2 边沿JK触发器

图13 由主从D触发器构造JK边沿触发器

因为JK触发器的两个输出端为互补输出,所以边沿JK触发器由一个主从D触发器即可构成,如图13所示。需要指出,图13(a)所示卡诺图中,蓝绿色圆边矩形所包含的是为避免图13(c)所示组合逻辑电路出现“竞争-冒险”现象而插入的冗余项。

4.3 边沿T触发器

图14 由主从D触发器构造T边沿触发器

「艾尔登法环」梅琳娜手办开订 立体手办▪

万代「艾尔登法环」白狼战鬼手办开订 立体手办▪

「夏目友人帐」猫咪老师粘土人开订 立体手办▪

「五等分的新娘∬」中野三玖·白无垢版手办开订 立体手办▪

「海贼王」乌索普Q版手办开订 立体手办▪

良笑社「初音未来」新手办开订 立体手办▪

「黑岩射手DAWN FALL」死亡主宰手办开订 立体手办▪

「盾之勇者成名录」菲洛手办登场 立体手办▪

「魔法少女小圆」美树沙耶香手办开订 立体手办▪

「咒术回战」七海建人粘土人登场 立体手办▪

「五等分的新娘」中野二乃白无垢手办开订 立体手办▪

「为美好的世界献上祝福!」芸芸粘土人开订 立体手办▪

「公主连结 与你重逢」六星可可萝手办开订 立体手办▪

「女神异闻录5」Joker雨宫莲手办开订 立体手办▪

「间谍过家家」约尔・福杰粘土人登场 立体手办▪

「街角魔族 2丁目」吉田优子手办开订 立体手办▪

「火影忍者 疾风传」旗木卡卡西·暗部版粘土人登场 立体手办▪

「佐佐木与宫野」宫野由美粘土人开订 立体手办▪

「盾之勇者成名录」第2季拉芙塔莉雅手办开订 立体手办▪

「咒术回战」两面宿傩Q版坐姿手办开订 立体手办▪

「DATE·A·BULLET」时崎狂三手办开订 立体手办▪

「狂赌之渊××」早乙女芽亚里粘土人开订 立体手办▪

「魔道祖师」魏无羨粘土人开订 立体手办▪

「新·奥特曼」奥特曼手办现已开订 立体手办▪